Leistungsstarke Tests und Messungen bis 100G Line-Rate

mit COTS-Servern und Napatechs FPGA SmartNICs

Lösung

Erstellen Sie fortschrittliche Test- und Messlösungen mit COTS-Servern und Napatech FPGA SmartNICs

Die Napatech Link Capture Software unterstützt leistungsstarke Funktionen für Test- und Messapplikationen.

Die Napatech Link Capture Software unterstützt leistungsstarke Funktionen für Test- und Messapplikationen.

Hardware-Sende- und Empfangszeitstempel im Nanosekundenbereich ermöglichen präzise Messungen der Netzwerkverzögerung und des Jitters.

Die Napatech Link Capture-Software unterstützt ein fortschrittliches Schema für die Erzeugung von L2 und L3/L4 (IP/TCP/UDP) Tx-Prüfsummen und die Überprüfung von Rx-Prüfsummen.

All dies wird für 10G, 25G, 40G und 100G Netzwerkgeschwindigkeiten unterstützt.

Key Benefits

- Die FPGA-basierten SmartNICs von Napatech umfassen spezialisierte und leistungsstarke Test- und Messfunktionen auf Standard-COTS-Servern, die eine Standard-NIC übertreffen

- Präzise Messungen mit Hardware-Zeitstempeln

- Für jedes übertragene Paket kann die Applikation individuell steuern, wie die Prüfsummen generiert werden, was eine flexible Konfiguration ermöglicht

- Napatech garantiert Line-Rate-Empfang und -Sendung und vollen Durchsatz ohne Paketverlust für alle Paketgrößen

Anwendungsfall 1:

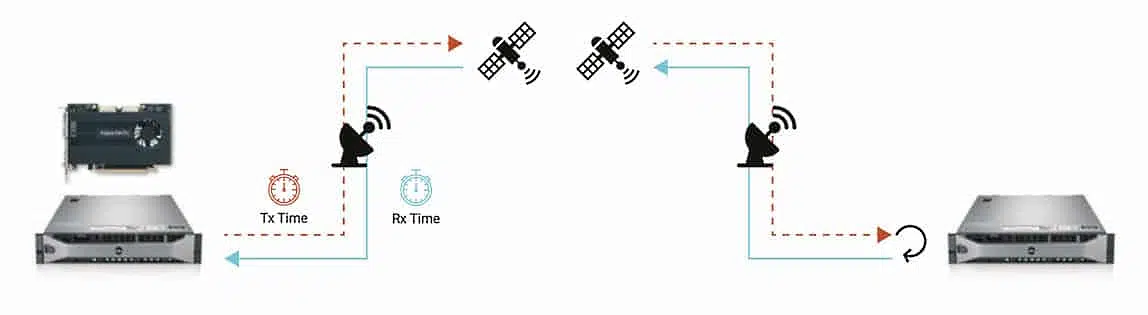

Messung der Roundtrip-Latenzzeit in Kommunikationsnetzen

Bei der Messung der Roundtrip-Latenzzeit ist es wichtig, einen genauen Zeitstempel sowohl für die gesendeten als auch für die empfangenen Pakete zu erhalten.

Die Generierung von Prüfsummen stellt eine Belastung für die Applikation dar und birgt die Gefahr einer Überlastung der CPUs. Eine Überlastung der CPUs beeinträchtigt die Performance des Gesamtsystems, insbesondere in 40G- oder 100G-Netzen.

Um die Herausforderungen der Messung der Roundtrip-Latenzzeit zu bewältigen, bieten die Napatech SmartNICs:

- Hochpräzise Start-of-Frame- oder End-of-Frame-Tx/Rx-Zeitstempel, abgetastet mit 1 Nanosekunde Auflösung

- L3/L4-Prüfsummengenerierung und -überprüfung für Latenzmessungen in gerouteten Netzen

- Erzeugen ungültiger L2/L3/L4-Prüfsummen zur Fehlersimulation

- Inter-Frame-Lückensteuerung pro Paket für Jitter-Simulation

Anwendungsfall 2:

Wiederholung des aufgezeichneten Datenverkehrs

zur Fehlersuche oder Simulation

Eine große Herausforderung bei bestehenden Paketerfassungssystemen sind die Performance-Anforderungen bei der präzisen Erfassung und Wiedergabe. Nicht nur die Genauigkeit des Zeitstempels ist eine Herausforderung, sondern auch die hohe Belastung der CPUs kann ein Problem darstellen.

Darüber hinaus kann es zu einer Beeinträchtigung der Performance kommen, wenn Verkehrsbündel bei vollem Durchsatz getestet werden, z. B. durch das Risiko von Paketverlusten und die mangelnde Präzision bei der Wiedergabe von Paketbündeln.

Um diese Capture-Replay-Herausforderungen zu lösen, bieten Napatech SmartNICs:

- Wiedergabe des Datenverkehrs genau so, wie er erfasst wurde, einschließlich exakter Zeitmessung, und Wiedergabe auch bei Fehlern

- Fehlersimulation durch Erzeugung von Paketen mit ungültigen Prüfsummen

- Flexible Prüfsummengenerierung und -überprüfung, die z. B. die Wiederholung mit geänderten IP-Adressen oder Port-Nummern ermöglicht

- Die Geschwindigkeit der Wiedergabe kann angepasst werden, um z.B. Burst-Verhalten zu simulieren. Die Wiedergabe kann entweder schneller oder langsamer sein als der aufgezeichnete Verkehr. Der Sendezeitstempel pro Paket kann von der Applikation gesteuert werden.

Anwendungsfall 3:

Traffic Generation

In verkehrserzeugenden Systemen müssen die Pakete mit Zeitstempelgenauigkeit gesendet und empfangen werden. Darüber hinaus belasten softwarebasierte Lösungen zur Generierung von Datenverkehr die CPUs stark, was die Performance des Gesamtsystems beeinträchtigt.

Der volle Hochgeschwindigkeitsdurchsatz, einschließlich des maximalen theoretischen Bursts, muss sowohl für den Paketempfang als auch für das Senden von Paketen gewährleistet sein.

Für die Verkehrserzeugung bieten Napatech SmartNICs:

- Beschleunigte Lösungen zur Verkehrserzeugung, z. B. mit dem Open-Source-Verkehrsgenerator TRex

- Prüfsummengenerierung und Prüfsummenüberprüfung

- Anwendung der Zeitstempelinjektion in Hardware

Ausgewählte Features

Hardware Timestamping

- 1 ns Zeitstempelauflösung

- Rx Timestamp

- Tx Timestamp injizieren

Tx Timestamp injizieren

- Anwendungsgesteuerte Aktion pro Paket

- Einfügen des Sendezeitstempels mit Versatz zum L3/L4-Header

- 8-Byte-Zeitstempel + 2 Byte für L3/L4-Prüfsummenkompensation (in Kombination mit der Erzeugung von L3/L4-Tx-Prüfsummen verwendet)

Erzeugung von L2 und L3/L4 (IP/TCP/UDP) Tx-Prüfsummen

- Anwendungsgesteuerte Aktion pro Paket

- Korrekte Prüfsumme generieren

- Falsche Prüfsumme generieren

- Prüfsumme unverändert lassen

Überprüfung von L2 und L3/L4 (IP/TCP/UDP) Rx-Prüfsummen

- Angabe gültig/ungültig im Paketdeskriptor und über API

- Filterung nach gültigen/ungültigen Prüfsummen

Eine vollständige Liste der Funktionen finden Sie in der Produktübersicht und in der Dokumentation.