Drastische Leistungsteigerung von Suricata auf 100Gbps

mittels High-Performance SmartNICs

Beschleunigung von Suricata mittels Napatech

zur zustandsabhängigen Flow-Verarbeitung

Suricata ist eine freie, quelloffene, ausgereifte, schnelle und robuste Engine zur Erkennung von Netzwerkbedrohungen. Die Suricata-Engine ist in der Lage, Intrusion Detection (IDS) in Echtzeit, Inline-Intrusion Prevention (IPS), Netzwerksicherheitsüberwachung (NSM) und Offline-PCAP-Verarbeitung durchzuführen.

Suricata inspiziert den Netzwerkverkehr mit Hilfe einer leistungsstarken und umfangreichen Regel- und Signatursprache und verfügt über eine leistungsstarke Lua-Skript-Unterstützung zur Erkennung komplexer Bedrohungen. Wenn eine Bedrohung oder ein anomales Verhalten erkannt wird, sendet Suricata eine Warnung an den Administrator und versucht optional, diese zu blockieren oder zu stoppen.

Die Zunahme des Netzwerkverkehrs und die immer raffinierteren Angriffsvektoren belasten die CPUs von IDS/IPS-Geräten enorm. Diese Systeme passen sich unter anderem dadurch an, dass ein größerer Teil der Paketverarbeitungsarbeit von der CPU auf ein FPGA-basiertes SmartNIC verlagert wird.

Es hat sich gezeigt, dass Napatech SmartNICs den verlustfreien Durchsatz von Suricata-Implementierungen drastisch erhöhen, indem sie Zero-Copy-DMA (Direct Memory Access) von Paketen direkt von der NIC zur Anwendung ermöglichen, wodurch CPU-Zyklen, die sonst für diese Aufgabe benötigt werden, frei werden.

Die neueste Suricata-Version kann auf eine noch höhere Leistung beschleunigt werden, indem eine Napatech SmartNIC angewiesen wird, einen erheblichen Teil der Paketverarbeitung im FPGA auf einer Pro-Flow-Basis zu verarbeiten, ohne dass der Datenverkehr auf der Host-CPU verarbeitet werden muss.

Suricata-Beschleunigung

Die Auswertung jedes Pakets in Echtzeit im Vergleich zu Tausenden von Angriffssignaturen für Hunderte oder Tausende von gleichzeitigen Daten-Flows würde enorme Rechenleistung erfordern. Um das Problem handhabbar zu machen, hat Suricata seit Version 3.2 den Administratoren die Möglichkeit gegeben, festzulegen, dass Verkehr, der bestimmten Kriterien entspricht, von der weiteren Analyse ausgeschlossen werden soll, sobald eine Entscheidung über die gewünschte Behandlung dieses Verkehrs getroffen wurde.

Dies ist eine Optimierung, die es den Paketen erlaubt, die volle Paketanalyse-Pipeline zu umgehen, sobald eine Pass/Drop-Entscheidung über den Verkehr getroffen wurde.

Zu den häufigen Situationen, in denen dieses „Umgehungs“-Merkmal angewandt wird, gehören

- Verschlüsselter Verkehr: Der Suricata Application Layer Parser hat die Fähigkeit, nach dem anfänglichen Handshake keine weitere Verarbeitung des verschlüsselten Datenverkehrs (TLS, IPsec, Kerberos) mehr zu erfordern.

- Streaming-Dienste: Wenn große Flows von bekannten Anbietern erwartet werden (z. B. Musik, Filme usw. von Netflix, YouTube, Spotify, Apple Music), kann der Verkehr je nach Richtlinie weitergeleitet oder blockiert werden, ohne dass jedes Paket entschlüsselt werden muss.

- Sonderfälle für bestimmte Verkehrsarten: Andere erwartete große Flows (z.B. ein Backup-Flow), oder wo bestimmte Hosts oder Anwendungen vertrauenswürdig sein können.

Verbesserung der Suricata-Leistung mittels Napatech SmartNIC

Netzwerk- und Sicherheitsanwendungen wie Suricata sind extrem CPU-intensiv und Flow-orientiert, aber es müssen nicht unbedingt alle Pakete zu jeder Zeit von der Anwendung verarbeitet werden. Nur die ersten paar Pakete in einem Daten-Flow können interessant sein, oder bestimmte Protokolle können ignoriert werden, oder nur Pakete zu/von bestimmten Personen können einer Überprüfung wert sein.

Die Napatech-Lösung verwendet eine Flow-basierte Aktionsverarbeitung zur vollständigen Umgehung von x86 (FWD, Blockieren, Umleiten) unter Verwendung eines arbeitslastspezifischen FPGAs für die Verarbeitung von Flow-Aktionen. Dies erfordert eine enge Integration zwischen x86-Anwendungen und SmartNICs über APIs, damit Anwendungen Aktionen auf einer Pro-Flow-Basis ändern können.

Die Grundidee eines Bypass besteht einfach darin, die Verarbeitung von Paketen, die keiner weiteren Prüfung bedürfen, so früh wie möglich in der Paketverarbeitungspipeline zu stoppen. Diese Funktion wird in der Suricata-Software aktiviert, indem das Schlüsselwort „Bypass“ in einer Regelsignatur verwendet wird, was bedeutet, dass, sobald ein Urteil gefällt wurde, der gesamte andere Verkehr im selben Flow sicher von der vollständigen Dekodierung und Auswertung ausgeschlossen werden kann.

Hier ist zum Beispiel eine Signatur zur Umgehung eines Daten-Flows, der mit der IP-Adresse übereinstimmt:

pass ip 1.2.3.4 any <> any any (msg:”pass all traffic from/to 1.2.3.4”; bypass; sid:1;)

Napatech erweitert diese Idee, indem es die SmartNIC-Hardware in die Lage versetzt, den umgeleiteten Datenverkehr auf dem FPGA ohne weitere Beteiligung von Suricata oder der Host-CPU zu verarbeiten. Ohne einen FPGA-basierten SmartNIC von Napatech wird diese Umgehung in Software durchgeführt. Wenn eine Napatech SmartNIC verwendet wird, wird die Umgehungsaktion auf der programmierbaren SmartNIC ausgeführt, wodurch die Leistung weiter erhöht und die Belastung der Allzweckprozessoren verringert wird.

Die Unterstützung für diese Funktion wurde kürzlich in das Suricata git-Repository integriert, das von der Open Information Security Foundation (OISF) verwaltet wird, und wird in allen zukünftigen Suricata-Versionen enthalten sein.

Die Implementierung basiert auf der Napatech Flow Management API, die es einer Anwendung ermöglicht, den Netzwerkverkehr auf einer Pro-Flow-Basis zu verfolgen, um einen Teil oder die gesamte Verarbeitung auf den SmartNIC-FPGA auszulagern: Die Analyse auf Anwendungsebene verbleibt auf den Host-CPUs, während die Pro-Paket-Aktionen in Hardware auf der Netzwerkschnittstellenkarte ausgeführt werden.

Die Flow Management API ist in der Lage, Netzwerk-Flows über den gesamten Lebenszyklus zu verwalten:

- Pflegen einer Tabelle der aktiven Flows

- Hinzufügen neuer Abläufe

- Ausführen von Aktionen pro Paket

- Synchronisieren von Paket-/Byte-Zählern

- Aktualisierung von Ablaufaufzeichnungen bei Abbruch oder Zeitüberschreitung

- Der Suricata-Quellcode bietet ein funktionierendes Beispiel der Napatech-API für Entwickler anderer Anwendungen.

Da die Napatech Flow Manager-Funktionalität in die Anwendungssoftware integriert ist, ist für Suricata-Anwender keine Programmierung erforderlich: Das hardwarebeschleunigte Flow-Management ist über die vertraute Suricata-Regelschnittstelle zugänglich. Um eine Flow-Bypass-Aktion in Hardware zu ermöglichen, muss Suricata lediglich mit Napatech-Unterstützung kompiliert und das Schlüsselwort „Bypass“ in die Regelsignatur aufgenommen werden.

Sobald Suricata feststellt, dass ein Daten-Flow umgangen werden kann, werden alle Pakete aus diesem Daten-Flow für die Dauer des Daten-Flows in der SmartNIC-Hardware behandelt. Dadurch werden die Host-CPUs von der Paketverarbeitung befreit, so dass die Anwendung einen höheren Durchsatz erzielen kann.

Demonstration der Umgehung der Hardware

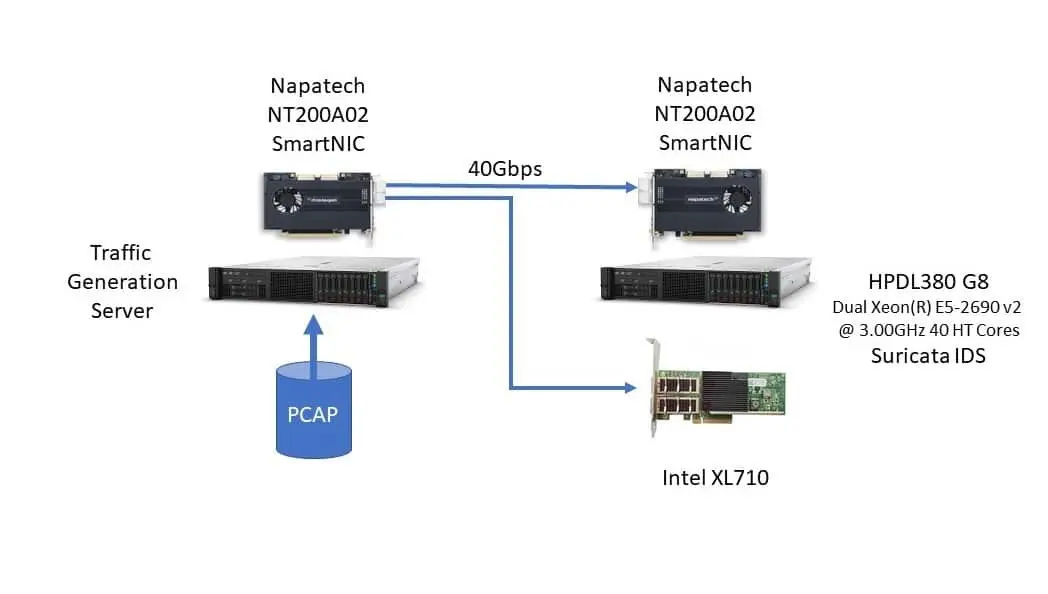

Um den Wert der Hardware-Umgehung zu veranschaulichen, vergleicht diese Demonstration den Durchsatz von Suricata auf einer Standard-NIC mit Software-Umgehung mit einer ansonsten identischen Konfiguration auf einer Napatech SmartNIC mit Zero-Copy Packet DMA und Hardware-Umgehung.

Hardware-Konfiguration

Die Testkonfiguration basierte auf einem HP DL380 G8 mit zwei Sockeln und Intel® Xeon® E5-2690 v2 3,0 GHz CPUs (40 HT-Kerne), auf denen CentOS 7.5 lief. Der Datenverkehr wurde durch die PCAP-Wiedergabe einer tatsächlichen Erfassung des Netzwerkverkehrs erzeugt, die eine Mischung aus TCP- (88 %) und UDP-Paketen (12 %) in über eine Million eindeutiger Flows umfasste.

Der Datenverkehr ist typisch für ein Unternehmensnetzwerk mit Hunderten von Benutzern, die Dutzende von interaktiven Client-Server-Anwendungen und Internetzugang ausführen.

Der Datenverkehr wurde von einer Napatech PCAP-Wiedergabeanwendung auf einem NT200 2x40GE SmartNIC bezogen und über 40 GE-Links zu dem zu testenden Gerät (DUT) geleitet, das entweder mit einem Napatech NT200 SmartNIC (2x40GE) oder einer Intel XL710 (1x40GE) Netzwerkschnittstellenkarte konfiguriert war.

Suricata-Konfiguration

Organisationen müssen ihre IDS/IPS fast immer kalibrieren, um zu erkennen, wie normaler Datenverkehr im Netzwerk im Vergleich zu potenziell böswilligen Aktivitäten aussieht. Diese Anpassungen beinhalten eine Feinabstimmung des Regelsatzes und die Ermöglichung einer Umgehung nach Bedarf. Wie oben erwähnt, aktiviert der Benutzer die Umgehung durch Verwendung des Schlüsselworts „Bypass“ in einer Suricata-Regelsignatur.

In diesem Test wurde dem Suricata-Basisregelsatz eine einzige Umgehungsregel hinzugefügt. Die Syntax der zusätzlichen Regel lautet wie folgt:

drop tcp any [!80,! 20,!21,!23,!25,!53,!67,! 68] <> any (msg: „SURICATA Test rule“; priority:1;classtype:protocol-command-decode; bypass; sid:1000001; rev:2;)

In Worten: Diese Regel besagt, dass jeglicher TCP-Verkehr umgangen werden sollte, mit Ausnahme des Verkehrs zu/von dem angegebenen Satz von Port-Nummern. Die gleiche Art von Regel könnte leicht eine ähnliche Art der Umgehung für UDP-Verkehr, Verkehr zu/von einem Satz von Adressen, spezifischen Anwendungsprotokollen usw. bieten.

Mit dem im Test verwendeten Verkehrsmuster wurde der Effekt erreicht, dass etwa 70% des Verkehrs umgangen wurden und die restlichen 30% des Verkehrs vollständig von Suricata-Software auf den Host-CPUs abgewickelt wurden. Das SmartNIC stellt der Anwendung in diesem Fall immer noch Null-Kopie-DMA zur Verfügung, aber jeder Daten-Flow muss dekodiert, wieder zusammengesetzt und vollständig in Software verarbeitet werden.

In einer praktischen Anwendung könnte der Umfang des Umgehungsverkehrs von Null bis 100% reichen, und je mehr Verkehr auf das SmartNIC ausgelagert wird, desto höher ist die potenzielle Kapazität des Systems.

Testergebnisse

Für ein IDS/IPS ist eine verlustfreie Leistung eine absolute Voraussetzung für maximale Sicherheit. Tests haben gezeigt, dass ein Paketverlust von nur 3 % zu 10 % verpassten Alarmen führen kann; ein Paketverlust von nur 0,4 % kann eine Fehlerrate von 10 % bei der Dateiextraktion verursachen.

Bei diesem Test war der verlustfreie Durchsatz mit Hardware-Bypass auf dem Napatech SmartNIC 2,5-mal höher als beim gleichen Test mit einem Standard-NIC und Bypass in Software.

Gemessener verlustfreier Suricata-Durchsatz:

- IPS mit dem Emerging Threats Open Ruleset ohne Umgehung: 15 Gbps

- IPS unter Verwendung des Emerging Threats Open Ruleset mit Software-Umgehung: 30 Gbps

- IPS unter Verwendung des Emerging Threats Open Ruleset mit SmartNIC-Hardware-Bypass: 76 Gbit/s

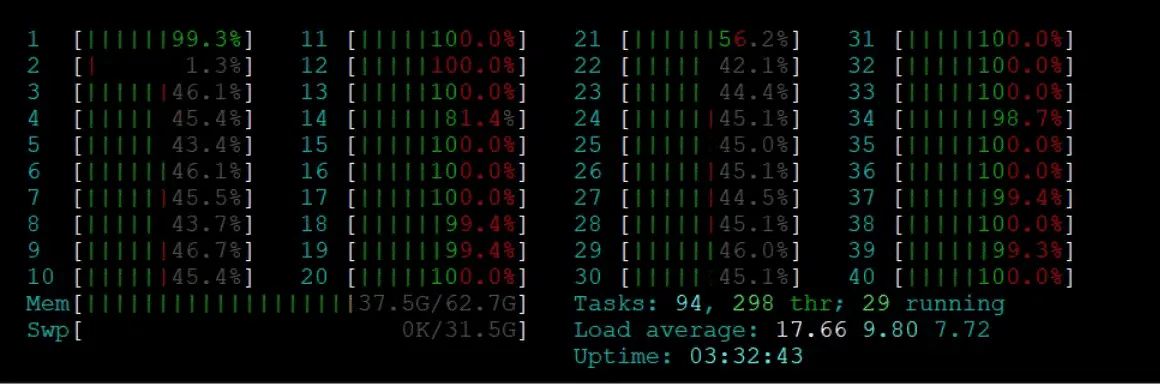

CPU-Auslastung

Bei der Standard-NIC war die Suricata-Arbeitslast sehr ungleichmäßig verteilt, wobei etwa die Hälfte der Cores mit einer Auslastung von 100 % lief, während andere Cores weniger als 50 % ausgelastet waren. Der Grund dafür ist, dass viele andere Lösungen eine asymmetrische Verkehrsverteilung oder eine Leistungseinbuße für nicht-lokalen Speicherzugriff aufweisen.

CPU-Auslastung (Standard-NIC)

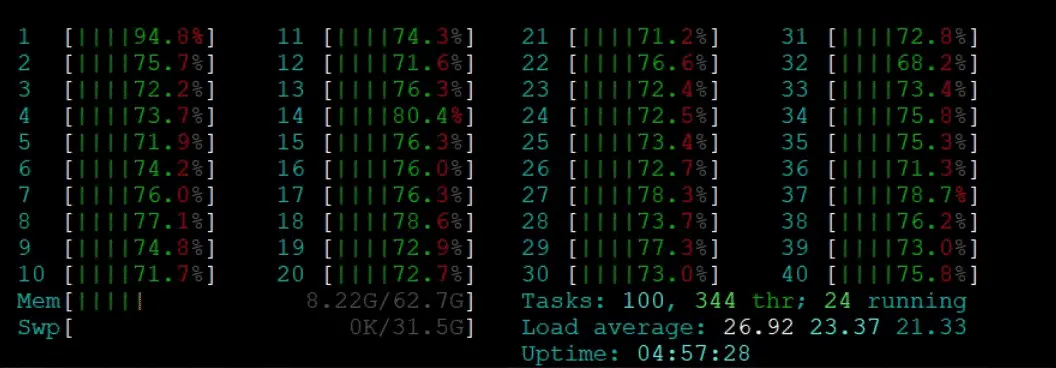

Auf dem Napatech SmartNIC war die Arbeitsbelastung viel gleichmäßiger über alle Kerne verteilt, wobei im Wesentlichen alle Kerne zu weniger als 80% ausgelastet waren.

CPU-Auslastung (Napatech SmartNIC)

Ein besser ausbalancierter Arbeitsablauf bedeutet eine höhere Systemeffizienz, da nicht einige wenige CPU-Kerne überlastet werden und keine Paketverluste verursachen, ohne dass das System voll ausgelastet ist.

Zusammenfassung

Dieser Test zeigt, dass Suricata 76 Gbps ohne Paketverlust verarbeitet, indem es den umgangenen Datenverkehr auf dem Napatech FPGA-basierten SmartNIC verarbeitet. Im Vergleich dazu erreicht dasselbe System, das die Umgehung in Software durchführt, einen Durchsatz von 30 Gbps ohne Paketverlust.

Darüber hinaus zeigte die Napatech-NIC eine Suricata-Arbeitslast, die über alle verfügbaren CPU-Kerne im System verteilt war, wodurch Prozessorausfälle oder Überlastungen mit Pufferüberlauf minimiert wurden.

Die Suricata-Hardware-Bypass-Funktion und die Napatech Flow Manager-API werden mit der LinkTM Capture- und LinkTM Inline-Software von Napatech auf der FPGA-basierten SmartNIC-Hardware NT200A02 und NT50B01 unterstützt.

Technische Spezifikationen

SmartNIC Hardware-Feature Highlights

| Allgemeine Hardware-Spezifikationen | NT200A02 | NT50B01 |

|---|---|---|

| Abmessungen | 1⁄2-Länge, volle Höhe PCIe | 1⁄2-Länge, 1⁄2-Höhe PCIe |

| Netzwerk-Ports | 2×QSFP28 | 2xSFP28 |

| Datenrate | 8×10Gbps,2×10/25Gbps, 4×10/25Gbps,2×40Gbps, 2×100Gbps |

2×10/25 Gbps |

| Onboard-Speicher | 12GB | 10 GB |

| PCIe-Konfiguration | 16-spurig 8 GT/s PCIe Gen3 | 16-spurig 8 GT/s PCIe Gen3 |

Gemeinsame Hardware-Feature Highlights

- Null Paketverlust für alle Frame-Größen von 64 Bytes bis 10.000 Bytes

- Fehlerhafte Frames behalten oder verwerfen

- Adressierung von bis zu 1 TB Anwendungspufferspeicher

- Paket- oder Segmentzustellung zur Anwendung

- Hardware-Beschleunigung für:

- Zusammenführen von Multi-Port-Paketen

- Lastverteilung über bis zu 128 CPU-Kerne

- Filterung basierend auf z.B. L3/L4-Kriterien

- Stateful-Flow-Management

- GTP-, IP-in-IP-, GRE- und NVGRE-Tunnel-Unterstützung

- Behandlung von IP-Fragmenten

- Slicing mit festem oder dynamischem Versatz

- De-Duplizierung in Hardware

- RMON1-Zähler, einschließlich Jumbo-Frames

- IEEE 1588-2008 PTP- und PPS-Zeitsynchronisation

- Hardware-Zeitstempel: Auflösung: 1 ns

- Stratum-3-konforme TCXO

- OS-Zeitsynchronisierung

Highlights der Napatech Software Suite

- NTAPI: Gemeinsame API für alle Napatech SmartNICs

- Einfache Programmierschnittstelle für schnelle Integration

- Null-Kopie-Übertragung von Daten zum Host

- Null-Kopie-Übertragung von Daten zwischen SmartNICs

- Paketbasierte Schnittstelle zur Abstraktion von Hardware-Details

- Stateful Flow-bewusste Match- und Aktionsverarbeitung

- Matching – die Abläufe sind auf der Grundlage eines flexiblen Schlüssel-Matchers vollständig konfigurierbar

- Aktionen

- Drop (Block) – Unerwünschter Verkehr wird gelöscht, wodurch die Systemressourcen reduziert und die Leistung erhöht werden

- Weiterleitung (Cut-Through/Bypass) – Lokal, auf der Karte, Port-zu-Port-Weiterleitung, reduziert CPU-Anforderungen und PCIe-Engpässe, senkt die Latenzzeit zur Steigerung der Anwendungsleistung

- Flow-based Load Balancing (RSS) – effiziente und verteilte CPU-Auslastung

- Pro Flow-Statistik (Pakete / Bytes) mit Richtungsstatus pro Paket

- Flow Aging – Überwachung des TCP-Flow-Status, konfigurierbare Timer für UDP

- Flow-Metadaten – Informationsaustausch zwischen Host-Anwendung und SmartNIC-Offload-Engine

- Erweiterte Funktionen einschließlich:

- Datenzusammenführung von Port-Daten aus mehreren SmartNICs zu einem einzigen Daten-Flow

- Gemeinsame Nutzung erfasster Daten zwischen mehreren Kundenanwendungen ohne die Notwendigkeit der Replikation

- Betriebssysteme: Linux, Windows

- ibpcap, WinPcap und DPDK

- IEEE 1588-2008 PTP-Stapel

- Im Quellcode enthaltene SDK-Werkzeuge zum Debuggen und Prototyping und als Anwendungsbeispiele